Editor : Vivado 2020.2

FPGA Board : Cmod A7-35t (xc7a35tcpg236-1)

AVR Board : ATmega128A

[요구 사항]

1. 선풍기 동작 구현

2. Button PUSH -> Buzzer ON

3. Button1 PUSH : 정지 Button2 PUSH : 약풍 Button3 PUSH : 강풍

4. Button PUSH -> FND 출력 (0,1,2)

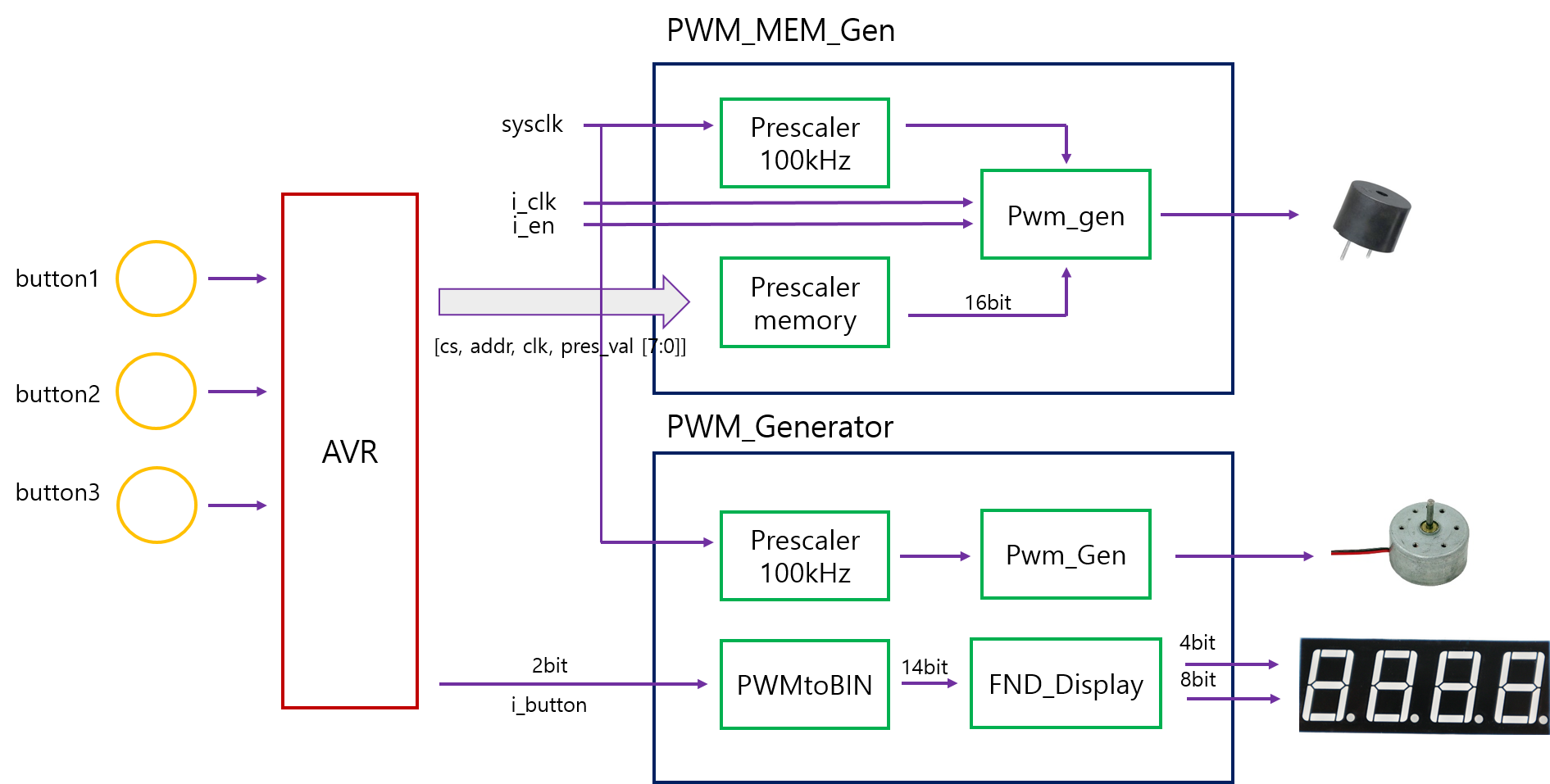

1. 구조 다이어그램

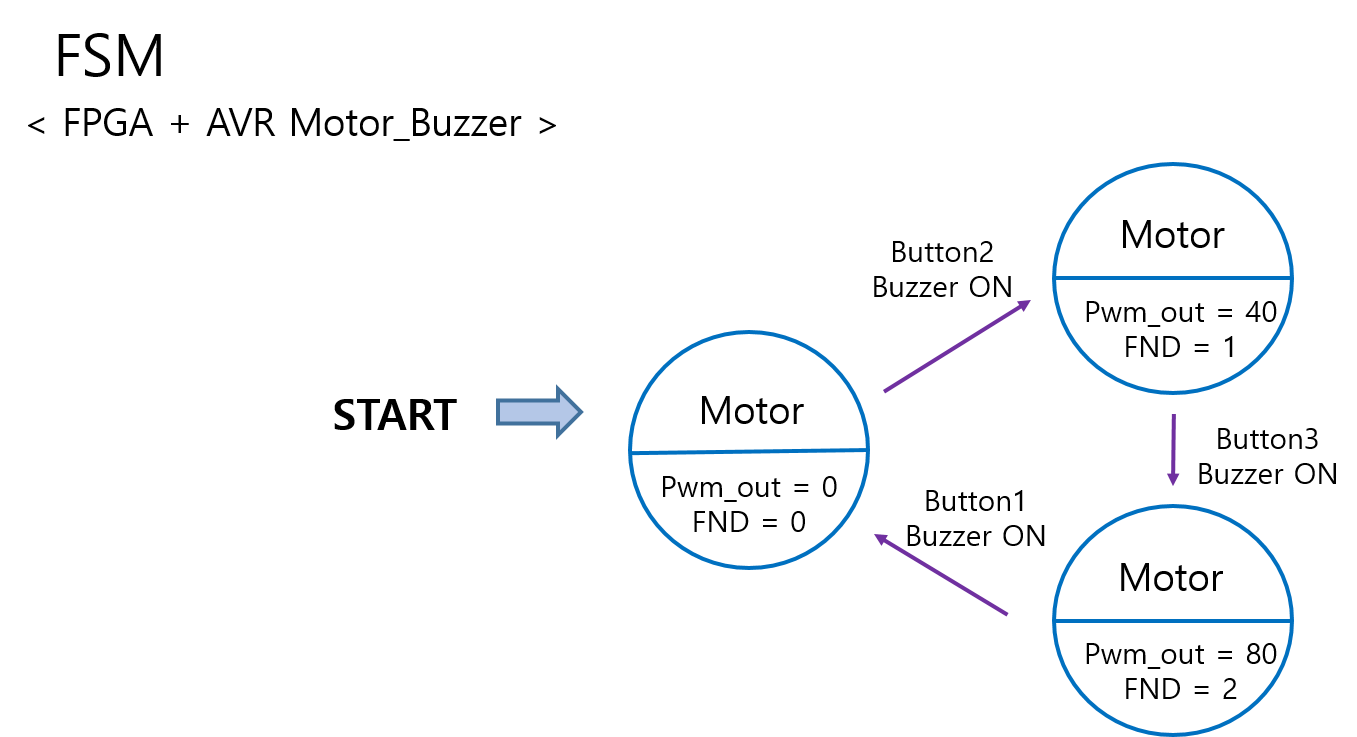

2. FSM

3. Vivado Top CODE

`timescale 1 ps / 1 ps

module handHeldFan

(i_addr,

i_clk,

i_cs,

i_en,

i_pres_value,

i_rst_n,

i_sw,

o_buzzer_clk,

o_fndFont,

o_fndSelect,

o_motor_clk,

sysclk);

input i_addr;

input i_cs;

input i_en;

input [7:0]i_pres_value;

input [1:0]i_sw;

output [3:0]o_fndSelect;

output o_motor_clk;

input sysclk;

wire [7:0]PWM_Generator_0_o_fndFont;

wire [3:0]PWM_Generator_0_o_fndSelect;

wire PWM_Generator_0_o_pwm_out;

wire PWM_MEM_Gen_0_o_pwm_clk;

wire i_addr_0_1;

wire i_clk_0_1;

wire i_cs_0_1;

wire i_en_0_1;

wire [7:0]i_pres_value_0_1;

wire i_rst_n_0_1;

wire [1:0]i_sw_0_1;

wire sysclk_0_1;

assign i_addr_0_1 = i_addr;

assign i_clk_0_1 = i_clk;

assign i_cs_0_1 = i_cs;

assign i_en_0_1 = i_en;

assign i_pres_value_0_1 = i_pres_value[7:0];

assign i_rst_n_0_1 = i_rst_n;

assign i_sw_0_1 = i_sw[1:0];

assign o_buzzer_clk = PWM_MEM_Gen_0_o_pwm_clk;

assign o_fndFont[7:0] = PWM_Generator_0_o_fndFont;

assign o_fndSelect[3:0] = PWM_Generator_0_o_fndSelect;

assign o_motor_clk = PWM_Generator_0_o_pwm_out;

assign sysclk_0_1 = sysclk;

handHeldFan_PWM_Generator_0_0 PWM_Generator_0

(.i_rst_n(i_rst_n_0_1),

.i_sw(i_sw_0_1),

.o_fndFont(PWM_Generator_0_o_fndFont),

.o_fndSelect(PWM_Generator_0_o_fndSelect),

.o_pwm_out(PWM_Generator_0_o_pwm_out),

.sysclk(sysclk_0_1));

handHeldFan_PWM_MEM_Gen_0_0 PWM_MEM_Gen_0

(.i_addr(i_addr_0_1),

.i_clk(i_clk_0_1),

.i_cs(i_cs_0_1),

.i_en(i_en_0_1),

.i_pwm_value(i_pwm_value_0_1),

.o_pwm_clk(PWM_MEM_Gen_0_o_pwm_clk),

.sysclk(sysclk_0_1));

endmodule

4. AVR main.c CODE

#define F_CPU 16000000UL

#include <avr/io.h>

#include <util/delay.h>

#include "button.h"

#define PWM_ADDR_DDR DDRD

#define PWM_ADDR_PORT PORTD

#define PWM_DATA_DDR DDRF

#define PWM_DATA_PORT PORTF

#define PWM_CLK_DDR DDRD

#define PWM_EN_DDR DDRD

#define PWM_CS_DDR DDRD

#define PWM_CLK_PORT PORTD

#define PWM_EN_PORT PORTD

#define PWM_CS_PORT PORTD

#define PWM_SW0_DDR DDRD

#define PWM_SW0_PORT PORTD

#define PWM_SW1_DDR DDRD

#define PWM_SW1_PORT PORTD

#define PWM_ADDR 0

#define PWM_CLK 1

#define PWM_EN 2

#define PWM_CS 3

#define PWM_SW0 4

#define PWM_SW1 5

void pwmInit()

{

PWM_ADDR_DDR |= (1<<PWM_ADDR);

PWM_DATA_DDR = 0xff;

PWM_CLK_DDR |= (1<<PWM_CLK);

PWM_EN_DDR |= (1<<PWM_EN);

PWM_CS_DDR |= (1<<PWM_CS);

PWM_SW0_DDR |= (1 << PWM_SW0);

PWM_SW1_DDR |= (1 << PWM_SW1);

}

#define ON 1

#define OFF 0

void buzzerSound(uint8_t onOff)

{

if(onOff == ON)

{

PWM_EN_PORT |= (1<<PWM_EN);

}

else

{

PWM_EN_PORT &= ~(1<<PWM_EN);

}

}

void buzzerHzValue(uint16_t hz)

{

PWM_CS_PORT &= ~(1<<PWM_CS);

PWM_ADDR_PORT = (PWM_ADDR_PORT & 0xfe) | 0;

PWM_DATA_PORT = (uint8_t)hz;

PWM_CLK_PORT &= ~(1<<PWM_CLK);

PWM_CLK_PORT |= (1<<PWM_CLK);

PWM_CLK_PORT &= ~(1<<PWM_CLK);

PWM_ADDR_PORT = (PWM_ADDR_PORT & 0xfe) | 1;

PWM_DATA_PORT = (uint8_t)(hz>>8);

PWM_CLK_PORT &= ~(1<<PWM_CLK);

PWM_CLK_PORT |= (1<<PWM_CLK);

PWM_CLK_PORT &= ~(1<<PWM_CLK);

PWM_CS_PORT |= (1<<PWM_CS);

}

int main(void)

{

pwmInit();

while (1)

{

if(getButton1State())

{

PWM_SW0_PORT &= ~(1<<PWM_SW0);

PWM_SW1_PORT &= ~(1<<PWM_SW1);

buzzerSound(ON);

buzzerHzValue(1000);

_delay_ms(500);

buzzerSound(OFF);

}

else if(getButton2State())

{

PWM_SW0_PORT |= (1<<PWM_SW0);

PWM_SW1_PORT &= ~(1<<PWM_SW1);

buzzerSound(ON);

buzzerHzValue(4000);

_delay_ms(500);

buzzerSound(OFF);

}

else if(getButton3State())

{

PWM_SW0_PORT &= ~(1<<PWM_SW0);

PWM_SW1_PORT |= (1<<PWM_SW1);

buzzerSound(ON);

buzzerHzValue(7000);

_delay_ms(500);

buzzerSound(OFF);

}

}

}

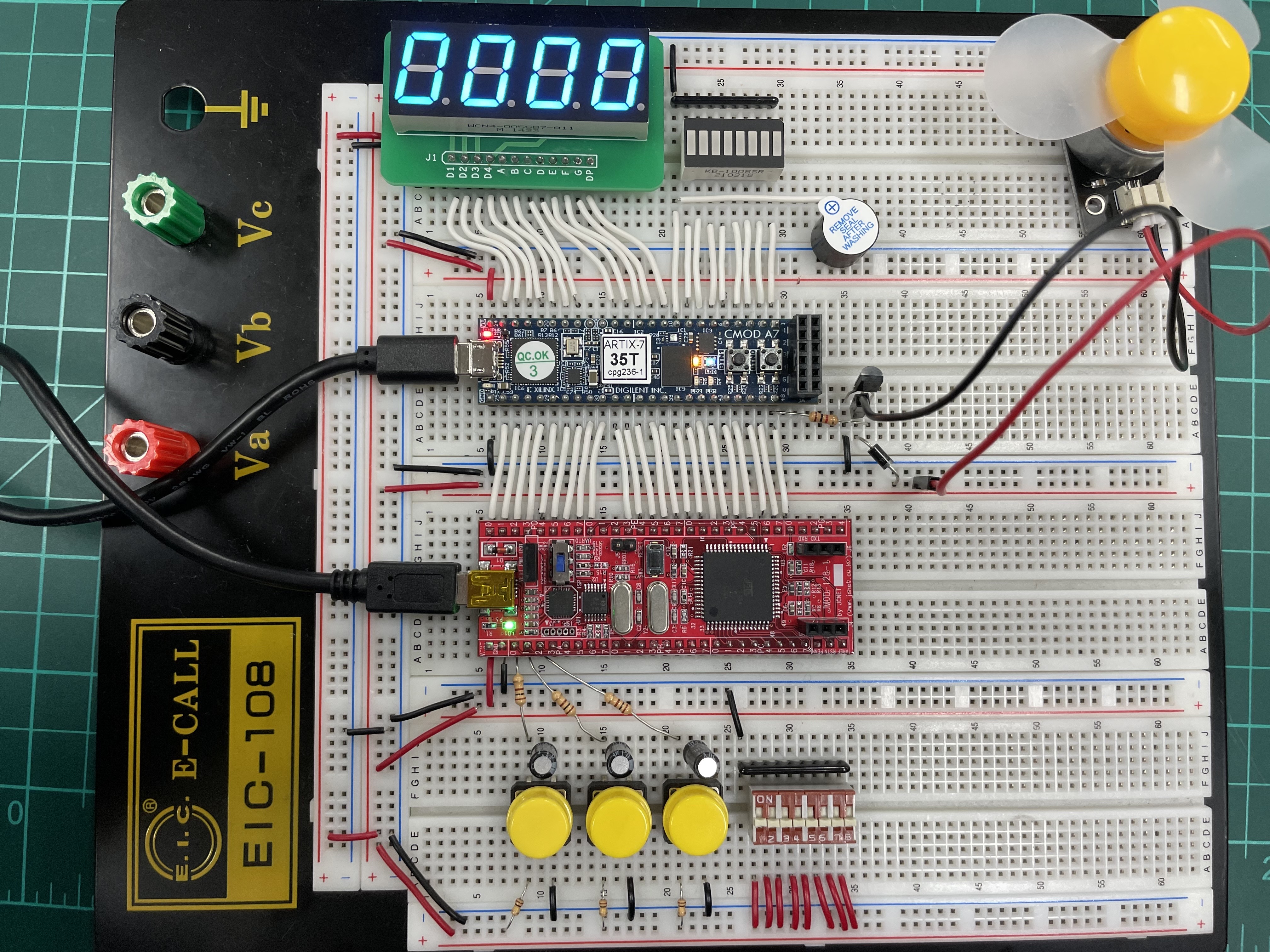

5. 동작영상 및 사진

'FPGA' 카테고리의 다른 글

| [FPGA] FPGA 보드에 CPU Core 올리기 (0) | 2021.11.15 |

|---|---|

| [FPGA] AVR+FPGA+LCD Shift register 설계 (0) | 2021.11.12 |

| [FPGA] Prescale Memory + Buzzer (0) | 2021.11.10 |

| [FPGA] FPGA + AVR 연동 UpCounter (0) | 2021.11.09 |

| [FPGA] IP Package 하기 (0) | 2021.11.09 |